Oficiální dokument AMD: Zen 5 má IPC zlepšené o 10–15+ %, jádro má 6 ALU a 512bitové SIMD

Před 2 roky

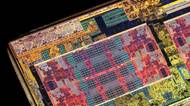

Teď asi nejdychtivějši očekávanou hardwarovou událostí jsou nadcházející procesory AMD Ryzen generace 8000, v nichž má mít premiéru nová architektura Zen 5. To má podle některých zvěstí být největší upgrade CPU jádra od prvního Zenu z roku 2017. Co toto nové jádro přinese, bylo dosud zastřeno tajemstvím, ale teď nastal první velký a důvěryhodně působící únik, který ho odhaluje. A dokonce nastřeluje i procentuální nárůst IPC. K těmto informacím se nějak dostal Moore's Law is Dead, který na videu z pátku ukazuje slajdy z nějaké prezentace AMD představující budoucí architektury AMD – Zen 5 a také na něj navazující Zen 6 (který by měl být evolucí Zenu 5). V dokumentech je roadmapa jader x86 představující čtyři generace – Zen 3, Zen 4 a poté novinky Zen 5 a Zen 6. Dokument pravděpodobně vznikl někdy po vydání Zenu 4 minulý rok nebo nedlouho před ním. Uvádí Zen 5 na rok 2023 a Zen 6 na rok 2024, ale to asi sedí spíš k času dokončení architektur, ne k vydání procesorů. Zen 5: rozšíření jádra na 6 ALU, 512bitové SIMD Jádro Zen 6 je zdá se v souladu s dosud prosakujícími pověstmi výrazně posílené. Dokumenty ukazují, že výrazně rozšiřuje Out of Order Engine a zároveň prohlubuje fronty. Jádro má přidané vykonávací jednotky: zejména šest ALU místo dosavadních čtyř. Ale také poprvé máme čtyři Load / Store (AGU) pipeline místo tří. Všechny čtyři umí provádět čtení (takže počet load operací je až čtyři za cyklus), dvě z nich zápis. Kromě přidání další pipeline ale Load / Store část také má rozšíření datové šířky na dvojnásobek – 512 bitů, čímž se vyrovná jádrům Intelu. Propustnost dat mezi jádrem a subsystémem pamětí a cache tak bude dvojnásobná, což může hodně pomoci v HPC kódu a podobných intenzivních aplikacích. Toto souvisí s velkou změnou v SIMD a FPU. Podle slajdů jádro bude zřejmě mít již nativně 512bitové jednotky pro výpočet instrukcí AVX-512 v jednom průchodu, což by mělo výrazně zlepšit jejich výkon (uvidíme ale, zda to nepovede k nárůstům spotřeby a propadům taktů jako u Intelu). Zen 4 provádí většinu operací AVX-512 ve dvou průchodech. Plná 512bitová šířka ale možná bude jen ve výkonnější „tlusté“ verzi jádra. AMD evidentně opět plánuje úspornou / kompaktní verzi Zen 5c a je naznačeno, že ta by mohla zůstat 256bitová. Podle nákresu jádra bude SIMD a FPU jednotka opět asi mít koprocesorový charakter typický pro procesory AMD, se separátním schedulerem a fází rename vedle separátní celočíselné skalární části. Není řečeno, zda bude mít stejný počet pipeline jako dnes. Větší L1 cache a další změny Základní celočíselná část má svůj scheduler údajně více unifikovaný proti Zenu 3 a 4 (u těch má celočíselná část čtyři rozdělené schedulery) a celkově by snad jeho efektivní kapacita měla být větší. Také další fronty se mají zvětšit, což by mělo umožnit získat vyšší IPC. „Okno“ pro out-of-order optimalizaci má být „hluboké“ a znamená to asi, že se zvětší dosud poměrně malý ReOrder Buffer. Ale nevíme, jak moc. Pravděpodobně dostanou větší kapacitu také load a store fronty. Nevíme zatím, zda AMD přidá i na instrukčních dekodérech. Na jejich přidávání není asi takový tlak, protože architektury AMD se spoléhají na uOP cache, která dekodéry částečně obchází. Dispatch, který v Zenu 4 propouštěl šest operací za cyklus, byl ale rozšířen na osm a také fáze rename zvládne osm operací za cyklus. Fetch z instrukční cache by snad měl umět načítat dva různé bloky za cyklus. Ryzen 9 7950X s architekturou Zen 4 Autor: Ľubomír Samák Jádro má vylepšený prefetching dat a prediktor větvení (což jsou typicky věci, které se snaží vylepšit každé nové jádro). Podmíněné větvení má být jádro schopné zpracovat bez prostojů (bublin) v pipel